# DS3144DK Quad DS3/E3 Framer Demo Kit Daughter Card

# www.maxim-ic.com

# **GENERAL DESCRIPTION**

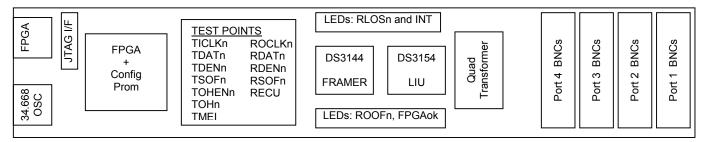

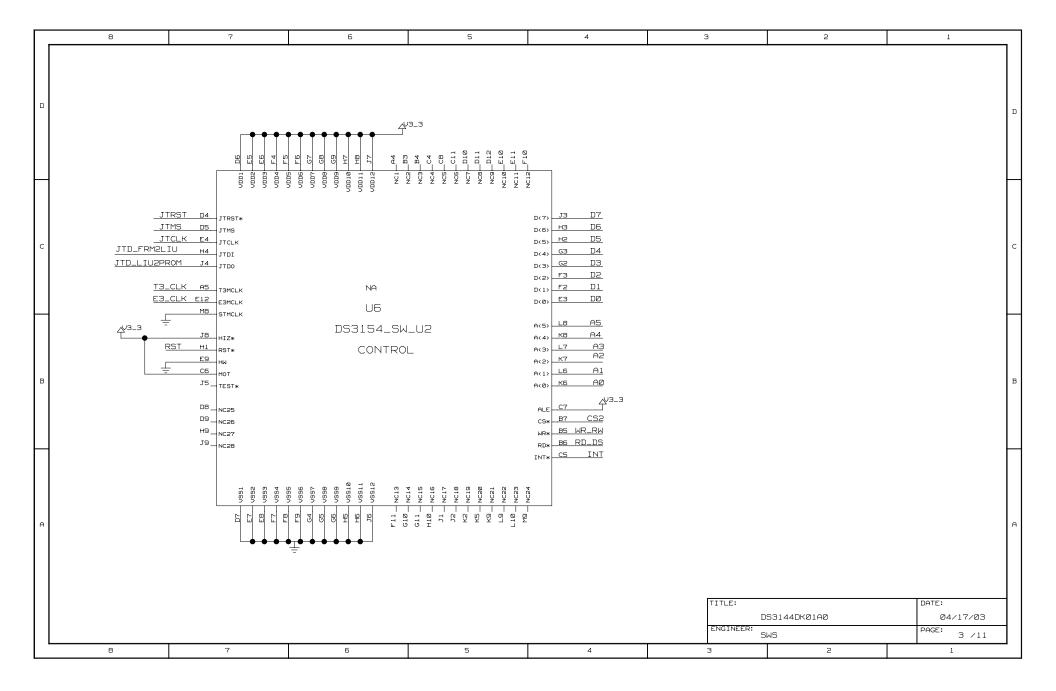

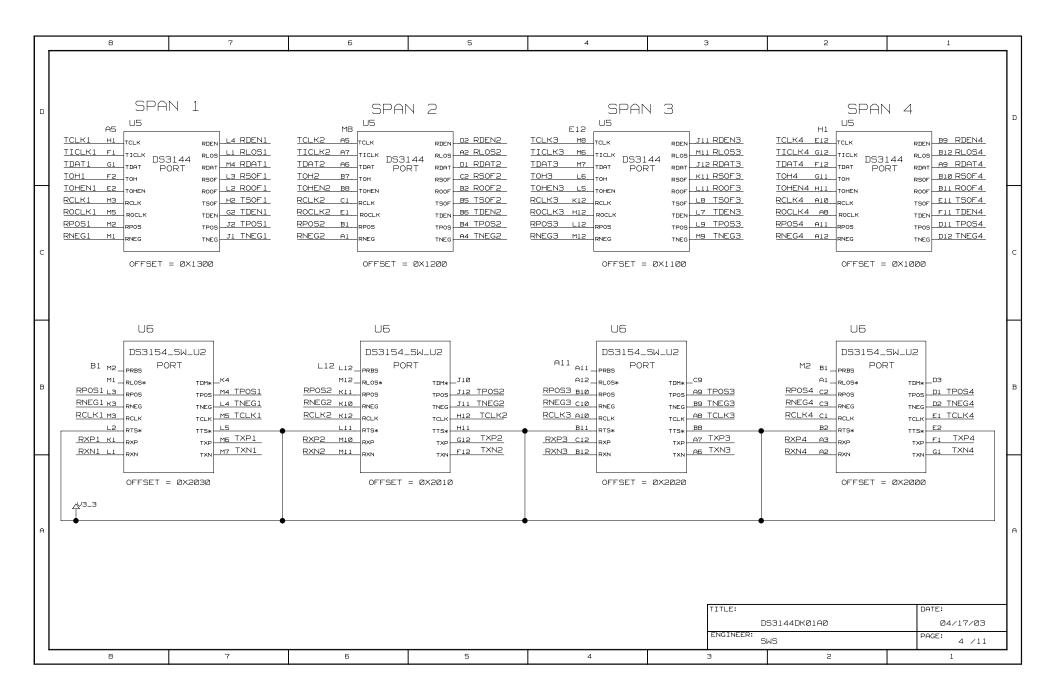

The DS3144DK is an easy-to-use evaluation board for the DS3144 quad DS3/E3 framer. It is intended to be used as a daughter card with the DK101 motherboard or the DK2000 motherboard. The DS3144DK comes complete with a DS3144 quad framer, DS3154 quad LIU, transformers, termination resistors, network connectors, and motherboard connectors. The DK101/DK2000 motherboard and Dallas' ChipView software give point-and-click access to configuration and status registers from a Windows®-based PC. On-board LEDs indicate loss-of-signal, out-of-frame, and interrupt status. An on-board FPGA contains mux logic to connect framer ports to one another or to the DK2000 in a variety of configurations.

Each DS3144DK is shipped with a free DK101 motherboard. For complex applications, the DK2000 high-performance demo kit motherboard can be purchased separately.

Windows is a registered trademark of Microsoft Corp.

#### **DEMO KIT CONTENTS**

DS3144DK Demo Kit Daughter Card DK101 Demo Kit Motherboard

Download from <a href="www.maxim-ic.com/DS3144DK">www.maxim-ic.com/DS3144DK</a>:

DS3144DK Data Sheet

DS3144DK Support Files

ChipView Software

# **FEATURES**

- Demonstrates Key Functions of DS3144 Quad DS3/E3 Framer

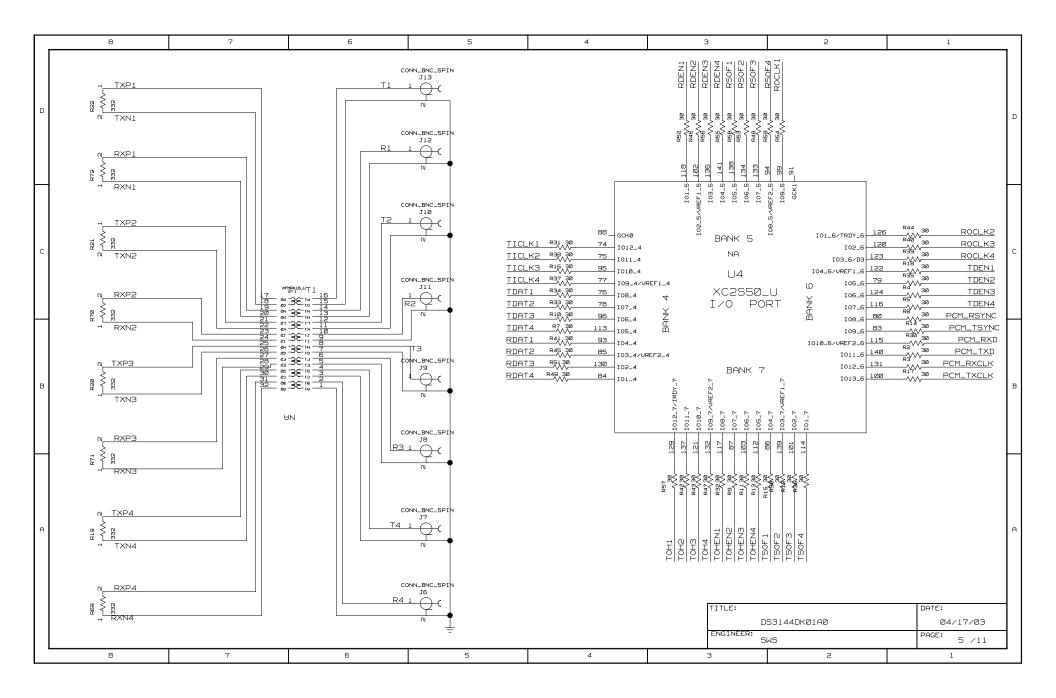

- Includes DS3154 Quad LIU, Transformers, BNC Connectors, and Termination Passives for Communication with Test Equipment over Coax

- Compatible with DK101 and DK2000 Demo Kit Motherboards

- DK101/DK2000 and ChipView Software Provide Point-and-Click Access to the DS3144 Register Set

- All Equipment-Side Framer Pins are Easily Accessible for External Data Source/Sink

- Memory-Mapped FPGA Provides Flexible Clock/Data/Sync Connections Among Framer Ports and DK2000 Motherboard

- LEDs for Out-of-Frame, Loss-of-Signal, and Interrupt

- Easy-to-Read Silk Screen Labels Identify the Signals Associated with all Connectors, Jumpers, and LEDs

# ORDERING INFORMATION

| PART     | DESCRIPTION                                                     |

|----------|-----------------------------------------------------------------|

| DS3144DK | DS3144 Demo Kit Daughter Card (with included DK101 motherboard) |

1 of 20 REV: 082203

# **COMPONENT LIST**

| DESIGNATION                                       | QTY | DESCRIPTION                                                                      | SUPPLIER                | PART                                    |

|---------------------------------------------------|-----|----------------------------------------------------------------------------------|-------------------------|-----------------------------------------|

| C1, C2, C15                                       | 3   | 0.1μF 10%, 16V ceramic capacitors (0805)                                         | Panasonic               | ECJ-2VB1C104K                           |

| C3–C9, C11–C14,<br>C16, C20, C22,<br>C23, C25–C32 | 23  | 0.1μF 10%, 16V ceramic capacitors (0603)                                         | Phycomp                 | 06032R104K7B20D                         |

| C10, C17, C18, C24                                | 4   | 1μF 10%, 16V ceramic capacitors (1206)                                           | Panasonic               | ECJ-3YB1C105K                           |

| C19, C21                                          | 2   | 10μF 20%, 10V ceramic capacitors (1206)                                          | Panasonic               | ECJ-3YB1A106M                           |

| DS1, DS3-DS10                                     | 9   | LED, red, SMD                                                                    | Panasonic               | LN1251C                                 |

| DS2                                               | 1   | LED, green, SMD                                                                  | Panasonic               | LN1351C                                 |

| J1                                                | 1   | 10-pin connector, dual-row vertical                                              | Digi-Key                | S2012-05-ND                             |

| J2–J5                                             | 4   | 20-pin headers, dual-row vertical                                                | Samtec                  | HDR-TSW-110-14-T-D                      |

| J6–J11                                            | 6   | 5-pin BNC connectors, right-angle vertical                                       | Cambridge               | CP-BNCPC-004                            |

| J12, J13                                          | 2   | 5-pin BNC connectors, right-angle                                                | Kruvand                 | UCBJR220                                |

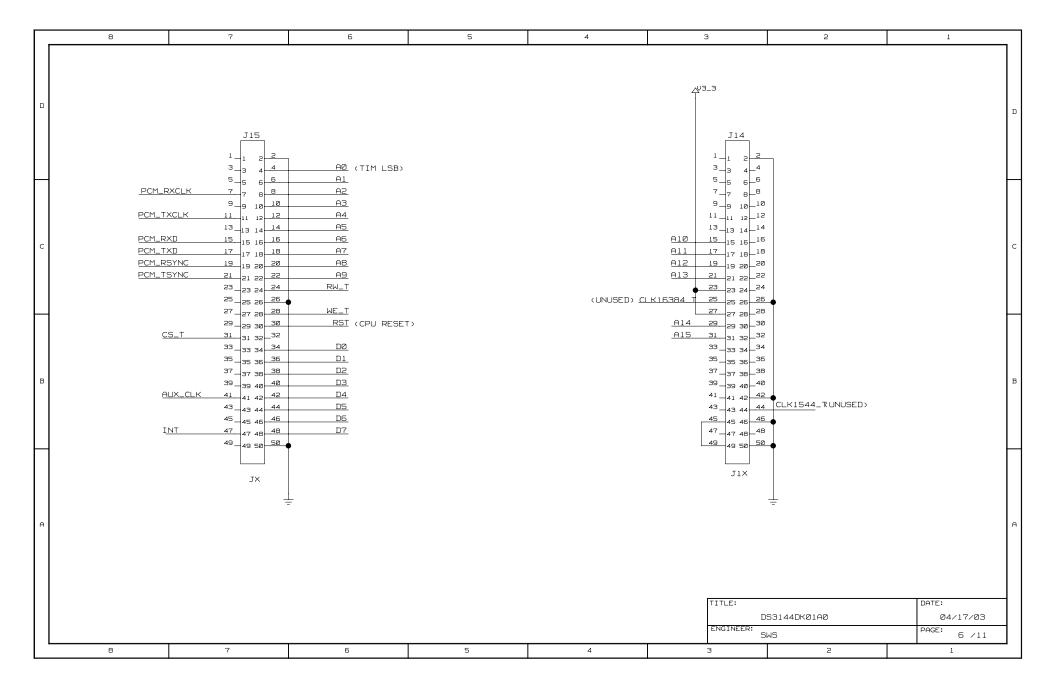

| J14, J15                                          | 2   | 50-pin connectors, dual-row vertical                                             | Samtec                  | TFM-125-02-S-D-LC                       |

| R1–R5, R7–R18,<br>R23, R28–R59                    | 49  | 30Ω 5%, 1/16W resistors (0603)                                                   | Panasonic               | ERJ-3GEYJ300V                           |

| R6                                                | 1   | 470Ω 5%, 1/10W resistor (0805)                                                   | Panasonic               | ERJ-6GEYJ471V                           |

| R19-R22, R69-R72                                  | 8   | 332Ω 1%, 1/10W resistors (0805)                                                  | Panasonic               | ERJ-6ENF3320V                           |

| R24                                               | 1   | 10kΩ 5%, 1/10W resistor (0805)                                                   | Panasonic               | ERJ-6GEYJ103V                           |

| R25, R26                                          | 2   | 330Ω 5% 1/10W MF resistors (0805)                                                | Panasonic               | ERA-6YEB331V                            |

| R27                                               | 1   | Not populated                                                                    | _                       | _                                       |

| R60                                               | 1   | 10kΩ 5%, 1/10W resistor (0805)                                                   | Panasonic               | ERJ-6ENF1002V                           |

| R61–R68                                           | 8   | 100Ω 1/16W 5% resistors (0603)                                                   | Panasonic               | ERJ-3GEYJ101V                           |

| T1                                                | 1   | XFMR, XMIT/RCV, 1 to 2, SMT 32-pin                                               | Pulse Engineering       |                                         |

| U1                                                | 1   | Serial configuration EEPROM for Xilinx, 65kB 8-pin DIP. Socketed (not populated) | Atmel                   | AT17LV65EUA and<br>61499-30831007000-ND |

| U2                                                | 1   | 1M PROM for FPGA<br>44-pin TQFP (not populated)                                  | Xilinx                  | XC18V01VQ44C_U                          |

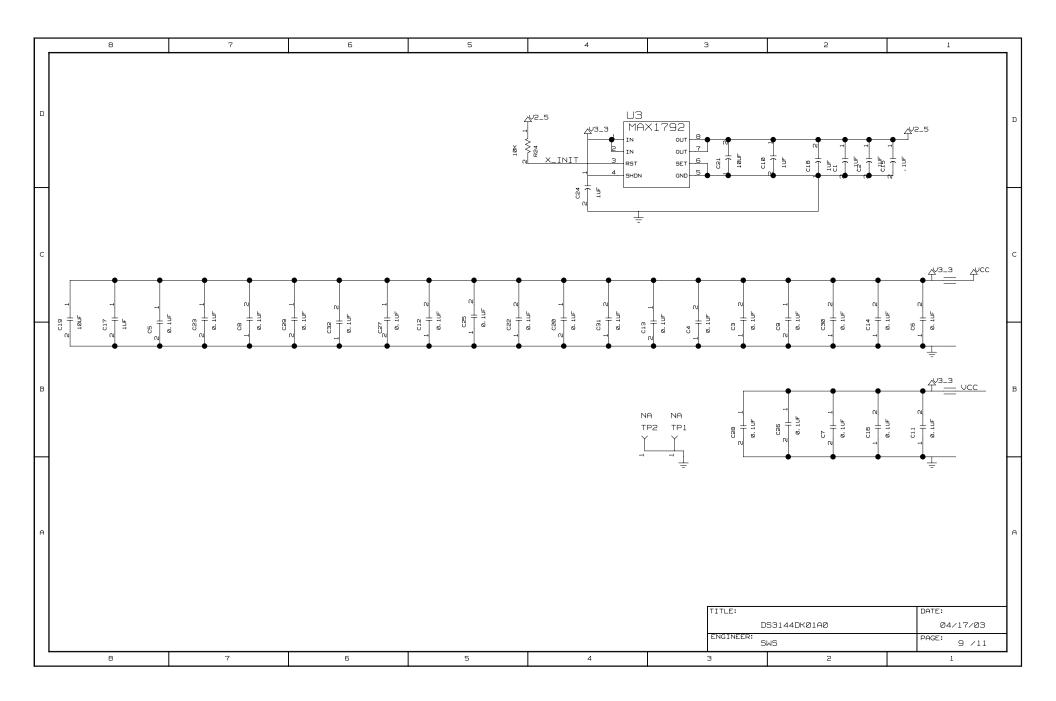

| U3                                                | 1   | 8-Pin $\mu$ MAX<br>V <sub>OUT</sub> = 2.5V or Adj                                | Maxim                   | MAX1792EUA25                            |

| U4                                                | 1   | Xilinx Spartan<br>2.5V FPGA, 20mm X 20mm 144-pin TQFP                            | Xilinx                  | XC2S50-5TQ144C                          |

| U5                                                | 1   | Quad DS3/E3 framer<br>144-pin BGA, 0°C to +70°C                                  | Dallas<br>Semiconductor | DS3144                                  |

| U6                                                | 1   | Quad DS3/E3/STS-1 LIU<br>144-pin BGA                                             | Dallas<br>Semiconductor | DS3154                                  |

| Y1                                                | 1   | 3.3V, 34.368MHz crystal clock oscillator                                         | SaRonix                 | NTH089AA3-34.368                        |

# **BOARD FLOORPLAN**

# LINE-SIDE CONNECTIONS

The DS3144DK implements the transmit (Tx) and receive (Rx) line interface networks recommended in the DS3154 data sheet. The BNC connectors are labeled TX1 through TX4 and RX1 through RX4. Note that the purpose of the DS3144DK is to evaluate the DS3144 framer, not the DS3154 LIU. The DS3144DK is not an impedance-matched board and therefore has not been designed to have transmit waveforms with optimal template fit. To evaluate the analog performance of the DS3154, request a DS3154DK demo kit.

# INTERFACE CONNECTORS

Two 50-pin connectors (J14, J15) on the bottom of the DS3144DK daughter card provide the processor interface, DS3 clock, and power supply from the DK101 or DK2000 motherboards. These connectors also provide a bidirectional clock/data/sync connection with the DK2000.

#### **CONNECTION TO A COMPUTER**

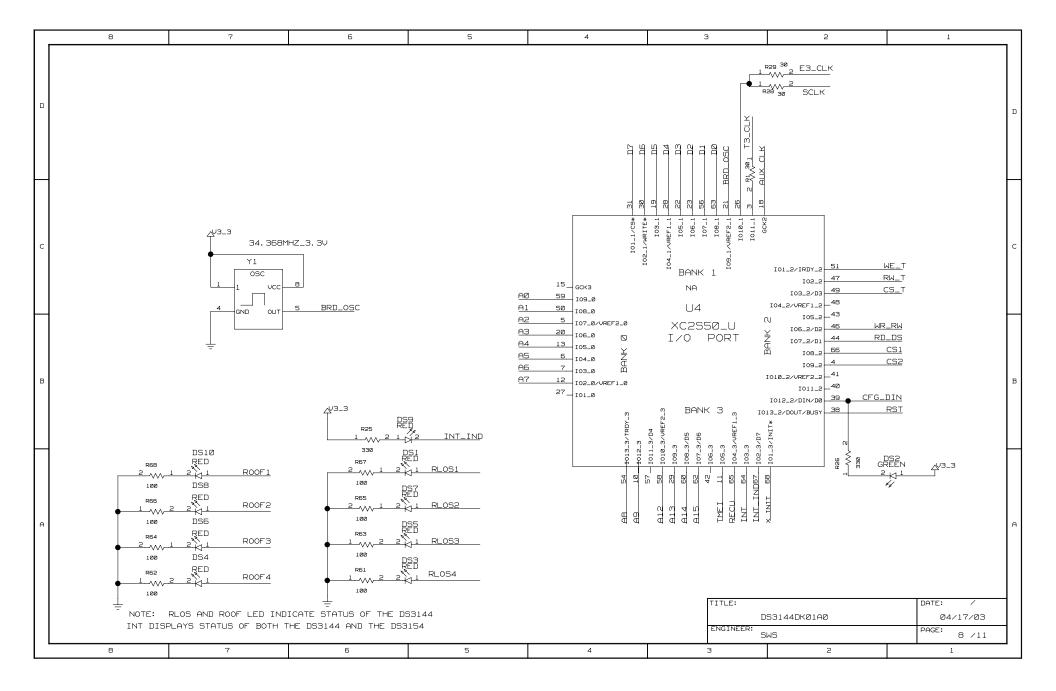

Refer to the DK101 data sheet or the DK2000 data sheet for information. After power is applied, if the DS3144DK is working correctly, the FPGA status LED (green) is lit, the INT LED (red) on the DS3144DK is not lit, and the RLOS and ROOF LEDs (red) may or may not be lit.

# **QUICK SETUP (REGISTER VIEW)**

- 1) Connect the DS3144DK daughter card to the DK101 motherboard or the DK2000 motherboard.

- 2) Connect the motherboard to a PC and a power supply as described in the motherboard data sheet.

- 3) Install and run the ChipView software, as described in the motherboard data sheet.

- 4) ChipView offers a choice between Register View, Demo, and Terminal Mode. Select Register View.

- 5) In the Definition File Assignment window, select the file DS3144DC\_FPGA.def. This definition file will, in turn, load DS3154DC.def, DS3144 1 DC.def, DS3144 2 DC.def, DS3144 3 DC.def, and DS3144 4 DC.def.

- 6) Next the Register View Screen appears, showing the register names, acronyms, and values for the DS3144, DS3154, and the FPGA. Select among the register views using the pulldown menu box on the right.

Several register initialization (.INI) files are available for the DS3144DK. Initialization files are loaded by selecting the menu option File→Register .INI File→Load .INI File.

- 7) Load the .INI file DS3144 1 txPRBS215-1 Cbit.ini.

- 8) Switch to the DS3154 register view (DS3154DC.def) and set TCR1 = 0 and RCR1 = 0 on the DS3154 (this clears the transmit tri-state and receive tri-state bits that are set on power-up in the DS3154).

- 9) Loopback port 1 by either (a) connecting a length of coax cable between the TX1 BNC and the RX1 BNC, or (b) setting the GCR1:LLB (local loopback) bit in the DS3154.

- 10) Switch to the DS3144 port 1 register view (DS3144\_1\_DC.def). Toggle BCR1:TC high then low to begin transmitting a 2<sup>15</sup> 1 PRBS pattern. Toggle BCR1:RESYNC high then low to resynchronize the BERT receiver.

- 11) At this point the following may be observed:

- Port 1 RLOS and ROOF LEDs are not lit, meaning the port 1 framer has acquired frame sync. This can also be observed in the port 1 T3E3SR status register.

- The port 1 BSR:SYNC bit is set, indicating the BERT receiver is receiving the 2<sup>15</sup> 1 PRBS pattern.

This is a very basic setup designed to build familiarity with the DS3144DK. Many other configurations are possible. Consult the DS3144 data sheet and the remainder of this data sheet for further information.

# **MEMORY MAP**

DK101 daughter card address space begins at 0x81000000.

DK2000 daughter card address space begins at:

0x30000000 for slot 0

0x40000000 for slot 1

0x50000000 for slot 2

0x60000000 for slot 3

All offsets in Table 1 below are relative to the beginning of the daughter card address space.

Table 1. Daughter Card Address Map

| DS3/E3<br>PORT NUMBER | DS3144 OFFSET    | DS3154 OFFSET    | FPGA OFFSET      |

|-----------------------|------------------|------------------|------------------|

| 1                     | 0x1300 to 0x13FF | 0x2030 to 0x203F | 0x0010 to 0x001F |

| 2                     | 0x1000 to 0x10FF | 0x2010 to 0x201F | 0x0020 to 0x002F |

| 3                     | 0x1100 to 0x11FF | 0x2020 to 0x202F | 0x0030 to 0x003F |

| 4                     | 0x1200 to 0x12FF | 0x2000 to 0x200F | 0x0040 to 0x004F |

All offsets in Table 2 below are relative to the daughter card address space plus the DS3/E3 port offset in Table 1.

Table 2. DS3144DK FPGA Register Map

| OFFSET | REGISTER | TYPE      | DESCRIPTION                     |  |  |

|--------|----------|-----------|---------------------------------|--|--|

| 0x0000 | BID      | Read-Only | Board ID                        |  |  |

| 0x0002 | XBIDH    | Read-Only | High Nibble Extended Board ID   |  |  |

| 0x0003 | XBIDM    | Read-Only | Middle Nibble Extended Board ID |  |  |

| 0x0004 | XBIDL    | Read-Only | Low Nibble Extended Board ID    |  |  |

| 0x0005 | BREV     | Read-Only | Board Fab Revision              |  |  |

| 0x0006 | AREV     | Read-Only | Board Assembly Revision         |  |  |

| 0x0007 | PREV     | Read-Only | PLD Revision                    |  |  |

| 0x000A | PCTC_SR  | Control   | PCM_TXCLK Source                |  |  |

| 0x000B | PCTS_SR  | Control   | PCM_TSYNC Source                |  |  |

| 0x000C | PCRX_SR  | Control   | PCM_RXD Source                  |  |  |

| 0x000D | PCRC_SR  | Control   | PCM_RXCLK Source                |  |  |

| 0x000E | PCRS_SR  | Control   | PCM_RSYNC Source                |  |  |

| 0x0010 |          |           |                                 |  |  |

| 0x0020 | TDAT_SR  | Control   | DS3144 TDAT Source              |  |  |

| 0x0030 | IDAI_OK  | Control   | DOST44 TDAT Source              |  |  |

| 0x0040 |          |           |                                 |  |  |

| 0x0011 |          |           |                                 |  |  |

| 0x0021 | TICK SR  | Control   | DS3144 TICLK Source             |  |  |

| 0x0031 | TICK_SIX | Control   | D33144 FIGER Source             |  |  |

| 0x0041 |          |           |                                 |  |  |

| 0x0012 |          |           |                                 |  |  |

| 0x0022 | TSOF_SR  | Control   | DS3144 TSOF Source              |  |  |

| 0x0032 | ISOF_SK  | Control   | D33144 130F 300108              |  |  |

| 0x0042 |          |           |                                 |  |  |

Registers in the FPGA can be easily modified using the ChipView software and the definition file named DS3144DC\_FPGA.def. Registers 0x00 through 0x07 (excluding register 0x01, which has no function on the DS3144DK) are read-only and are programmed at the factory to document board identification and revision information. The remaining registers in the FPGA control the connection of the DS3144's equipment-side framer pins. With these control registers, the framers within the DS3144 can be looped back on themselves externally, connected to each other back-to-back, or connected to the DK2000 motherboard.

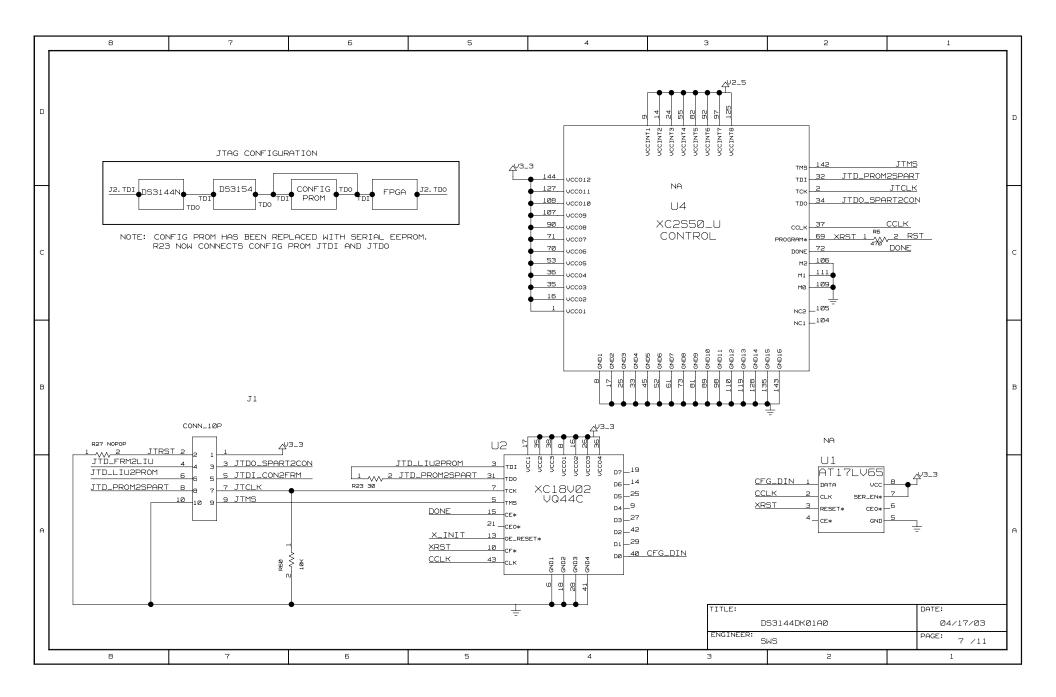

In <u>Table 2</u> and the control register descriptions below, PCM\_TXCLK, PCM\_TXD, and PCM\_TSYNC are clock/data/sync lines over which the DS3144 can transmit a DS3/E3 data stream to the DK2000 motherboard or other daughter cards plugged into the DK2000. PCM\_RXCLK, PCM\_RXD, and PCM\_RSYNC are clock/data/sync lines over which the DS3144DK can receive a DS3/E3 data stream from the DK2000 or a daughter card plugged into the DK2000. See the DS3144DK schematics for additional details.

Note that the DS3/E3 port numbers of the DS3144DK (as silk-screened on the board) do not match the DS3144 port numbers and the DS3154 port numbers. <u>Table 3</u> details the mapping of device port numbers to board port numbers. This mapping is reflected in the address ranges shown in <u>Table 1</u>.

Table 3. Relationship of Silk-Screened Port Numbers to IC Ports Numbers

| SILK-SCREENED PORT NUMBER<br>ON BNCs AND RLOS/ROOF LEDS | DS3144 PORT | DS3154 PORT |

|---------------------------------------------------------|-------------|-------------|

| 1                                                       | 4           | 4           |

| 2                                                       | 1           | 2           |

| 3                                                       | 2           | 3           |

| 4                                                       | 3           | 1           |

From this it can be seen that, for example, the BNCs and LEDs for DS3144DK port 4 are associated with port 3 of the DS3144 and port 1 of the DS3154.

# **CONTROL REGISTERS**

Register Name: PCTC\_SR

Register Description: PCM\_TXCLK Source

Register Address Offset: 0x0A

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---------|---|---|---|---|---|------|------|------|

| Name    | _ | _ | _ | _ | _ | PCS2 | PCS1 | PCS0 |

| Default | _ | _ | _ | _ | _ | 0    | 0    | 0    |

#### Bits 2 to 0: PCM TXCLK Source (PCS[2:0])

000 = Tri-state PCM TXCLK

001 = Drive PCM TXCLK with TDEN/TGCLK1

010 = Drive PCM TXCLK with TDEN/TGCLK2

011 = Drive PCM TXCLK with TDEN/TGCLK3

100 = Drive PCM\_TXCLK with TDEN/TGCLK4

Register Name: PCTS\_SR

Register Description: PCM\_TSYNC Source

Register Address Offset: 0x0B

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---------|---|---|---|---|---|------|------|------|

| Name    | _ | _ | _ | _ | _ | PSS2 | PSS1 | PSS0 |

| Default | _ | _ | _ | _ | _ | 0    | 0    | 0    |

#### Bits 2 to 0: PCM TSYNC Source (PSS[2:0])

000 = Tri-state PCM TSYNC

001 = Drive PCM TSYNC with TSOF1

010 = Drive PCM TSYNC with TSOF2

011 = Drive PCM\_TSYNC with TSOF3

100 = Drive PCM TSYNC with TSOF4

**Note:** Only use non-zero settings of PSS[2:0] when the TSOFx pin is configured as an output by setting MC3:TSOFC = 1 in the corresponding DS3144 framer.

Register Name: PCRX\_SR

Register Description: PCM\_RXD Source

Register Address Offset: 0x0C

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---------|---|---|---|---|---|-------|-------|-------|

| Name    | _ | _ | _ | _ | _ | PRXS2 | PRXS1 | PRXS0 |

| Default | _ | _ | _ | _ | _ | 0     | 0     | 0     |

# Bits 2 to 0: PCM\_RXD Source (PRXS[2:0])

000 = Tri-state PCM RXD

001 = Drive PCM\_RXD with RDAT1 010 = Drive PCM\_RXD with RDAT2 011 = Drive PCM\_RXD with RDAT3 100 = Drive PCM\_RXD with RDAT4

Register Name: PCRC\_SR

Register Description: PCM\_RXCLK Source

Register Address Offset: 0x0D

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---------|---|---|---|---|---|-------|-------|-------|

| Name    | _ | _ | _ | _ | _ | PRCS2 | PRCS1 | PRCS0 |

| Default | _ | _ | _ | _ | _ | 0     | 0     | 0     |

# Bits 2 to 0: PCM\_RXCLK Source (PRCS[2:0])

000 = Tri-state PCM RXCLK

001 = Drive PCM\_RXCLK with RDEN/RGCLK1 010 = Drive PCM\_RXCLK with RDEN/RGCLK2 011 = Drive PCM\_RXCLK with RDEN/RGCLK3 100 = Drive PCM\_RXCLK with RDEN/RGCLK4

Register Name: PCRS SR

Register Description: PCM\_RSYNC Source

Register Address Offset: 0x0E

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|---------|---|---|---|---|---|-------|-------|-------|

| Name    | _ | _ | _ | _ | _ | PRSS2 | PRSS1 | PRSS0 |

| Default | _ | _ | _ | _ | _ | 0     | 0     | 0     |

#### Bits 2 to 0: PCM RSYNC Source (PRSS[2:0])

000 = Tri-state PCM RSYNC

001 = Drive PCM RSYNC with RSOF1

010 = Drive PCM\_RSYNC with RSOF2

011 = Drive PCM\_RSYNC with RSOF3

100 = Drive PCM\_RSYNC with RSOF4

Register Name: TDAT\_SR

Register Description: DS3144 TDATx Source Register Address Offset: 0x10, 0x20, 0x30, 0x40

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2        | 1        | 0        |

|---------|---|---|---|---|---|----------|----------|----------|

| Name    | _ | _ | _ | _ | _ | TDS2     | TDS1     | TDS0     |

| Default | _ |   |   | _ |   | See note | See note | See note |

# Bits 2 to 0: TDATx Source (TDS[2:0])

000 = Tri-state TDATx

001 = Drive TDATx with RDAT1

010 = Drive TDATx with RDAT2

011 = Drive TDATx with RDAT3

100 = Drive TDATx with RDAT4

101 = Drive TDATx with PCM TXD

**Note:** Initial values are such that TDAT1←RDAT1, TDAT2←RDAT2, TDAT3←RDAT3, TDAT4←RDAT4, which corresponds to address 0x10 = 001, address 0x20 = 010, address 0x30 = 011, and address 0x40 = 100.

Register Name: TICK\_SR

Register Description: DS3144 TICLKx Source Register Address Offset: 0x11, 0x21, 0x31, 0x41

| Bit #   | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---------|---|---|---|---|---|------|------|------|

| Name    | _ | _ | _ | _ | _ | TCS2 | TCS1 | TCS0 |

| Default |   | _ | _ | _ | _ | 1    | 0    | 1    |

# Bits 2 to 0: TICLKx Source (TCS[2:0])

000 = Tri-state TICLKx

001 = Drive TICLKx with ROCLK1

010 = Drive TICLKx with ROCLK2

011 = Drive TICLKx with ROCLK3

100 = Drive TICLKx with ROCLK4

101 = Drive TICLKx with DS3\_CLK 110 = Drive TICLKx with E3\_CLK

... 2.... ... ... ... ... ... ... ...

Register Name: TSOF\_SR

Register Description: DS3144 TSOFx Source Register Address Offset: 0x12, 0x22, 0x32, 0x42

| Bit#    | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---------|---|---|---|---|---|------|------|------|

| Name    | _ | _ | _ | _ | _ | TSS2 | TSS1 | TSS0 |

| Default | _ | _ | _ | _ |   | 0    | 0    | 0    |

#### Bits 2 to 0: TICLKx Source (TSS[2:0])

000 = Tri-state TSOFx

001 = Drive TSOFx with RSOF1

010 = Drive TSOFx with RSOF2

011 = Drive TSOFx with RSOF3

100 = Drive TSOFx with RSOF4

**Note:** Only use non-zero settings of TSS[2:0] when the TSOFx pin is configured as an input by setting MC3:TSOFC = 0 in the corresponding DS3144 framer.

# **FPGA CONTROL EXAMPLES**

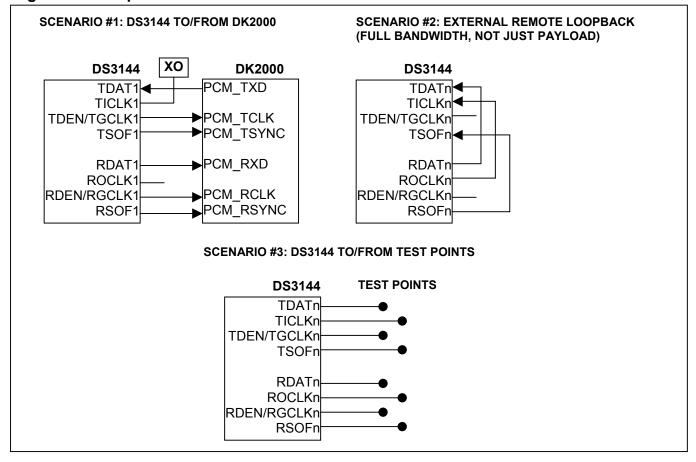

The control registers in the DS3144DK's FPGA support a number of different connection scenarios. <u>Figure 1</u> shows three example scenarios, and <u>Table 4</u> lists the FPGA control registers settings required to implement them.

Figure 1. Example Connection Scenarios

**Table 4. Register Settings for Sample Configurations**

| OFFSET(S) | REGISTER  | SCENARIO #1<br>(PORT 1 ONLY) | SCENARIO #2<br>(ALL PORTS) | SCENARIO #3<br>(ALL PORTS) |

|-----------|-----------|------------------------------|----------------------------|----------------------------|

| 0x000A    | PCTC_SR   | 001                          | N/A                        | N/A                        |

| 0x000B    | PCTS_SR   | 001                          | N/A                        | N/A                        |

| 0x000C    | PCRX_SR   | 001                          | N/A                        | N/A                        |

| 0x000D    | PCRC_SR   | 001                          | N/A                        | N/A                        |

| 0x000E    | PCRS_SR   | 001                          | N/A                        | N/A                        |

| 0x0010    | TDAT_SR   | 101                          | 001                        | 000                        |

| 0x0020    |           | N/A                          | 010                        | 000                        |

| 0x0030    |           | N/A                          | 011                        | 000                        |

| 0x0040    |           | N/A                          | 100                        | 000                        |

| 0x0011    | TICK_SR - | 101                          | 001                        | 000                        |

| 0x0021    |           | N/A                          | 010                        | 000                        |

| 0x0031    |           | N/A                          | 011                        | 000                        |

| 0x0041    |           | N/A                          | 100                        | 000                        |

| 0x0012    | TSOF_SR   | 000                          | 001                        | 000                        |

| 0x0022    |           | N/A                          | 010                        | 000                        |

| 0x0032    |           | N/A                          | 011                        | 000                        |

| 0x0042    |           | N/A                          | 100                        | 000                        |

# **DS3144 INFORMATION**

For more information about the DS3144 quad DS3/E3 framer, please consult the DS3144 data sheet, available on our website at <a href="https://www.maxim-ic.com/DS3144">www.maxim-ic.com/DS3144</a>.

# **DS3154 INFORMATION**

For more information about the DS3154 quad DS3/E3/STS-1 LIU, please consult the DS3154 data sheet, available on our website at <a href="https://www.maxim-ic.com/DS3154">www.maxim-ic.com/DS3154</a>.

# **DS3144DK INFORMATION**

For more information about the DS3144DK—including the ChipView software, the latest support files (.DEF, .INI, etc.), and the latest data sheet—please visit our website at <a href="https://www.maxim-ic.com/DS3144DK">www.maxim-ic.com/DS3144DK</a>.

# **DK101/DK2000 INFORMATION**

For more information about the DK101 or DK2000, please consult their respective data sheets, available on our website at <a href="https://www.maxim-ic.com/DK101">www.maxim-ic.com/DK101</a> or <a href="https://www.maxim-ic.com/DK2000">www.maxim-ic.com/DK2000</a>.

# **TECHNICAL SUPPORT**

For additional technical support, please email your questions to <a href="mailto:telecom.support@dalsemi.com">telecom.support@dalsemi.com</a>.

|    | 8                                                    | 7                              | 6                                                                                           | 5             | 4                                 | 3        |               | 2 | 1     |          |

|----|------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------|---------------|-----------------------------------|----------|---------------|---|-------|----------|

| ΙГ |                                                      |                                |                                                                                             | <u>'</u>      | !                                 | <u>'</u> | <del></del> , |   |       | 1        |

|    | *** Signal Cross-Reference                           | or the entire design ***       | NEG3 4B4<> 4C5<                                                                             | тхрз          | 4B3<> 5B8<                        |          |               |   |       |          |

|    | AØ 6D6<> BC5<                                        |                                | NEG4 4B2<> 4C2<<br>OCLK1 2C4<> 4CB> 5D2<                                                    | TXP4<br>WE_T  | 4B1<> 5AB<<br>5B5<> 8C1<>         |          |               |   |       |          |

|    | A1 6C6<> BC5<<br>A2 6C6<> BB5<                       |                                | OCLK2 2B4<> 4C6> 5C1<<br>OCLK3 2C2<> 4C5> 5C1<                                              | WR_RW<br>XRST | 8B1<> 2CB< 3B4<<br>7A3> 7A5> 7C2< |          |               |   |       | 1        |

| D  | A3 6C6<> 8B5<                                        | 2B8< 3B4<                      | OCLK4 2B2<> 4C2> 5C1<                                                                       | X_INIT        | 7A5<> 8A2<> 9D4<>                 |          |               |   |       |          |

| Н  | A4 6C6<> 8B5<<br>A5 6C6<> 8B5<                       | 288< 384< R                    | 00F1 4C7> 8A7<><br>00F2 4C5> 8A7<>                                                          |               |                                   |          |               |   |       | D        |

| 11 | A6 6C6<> 8B5<<br>A7 6C6<> 8B5<                       | 2A8< R                         | 00F3 4C3> 8A7<><br>00F4 4C1> 8A7<>                                                          |               |                                   |          |               |   |       |          |

| 11 | AB 5C5<> 8A4<<br>A9 5C5<> 8A4<                       | 2AB<                           | POS1 4B8<> 4C8< POS2 4B6<> 4C6<                                                             |               |                                   |          |               |   |       |          |

| 11 | A10 6C3<>                                            | R                              | P0S3 4B4<> 4C5<                                                                             |               |                                   |          |               |   |       | 1        |

| 11 | A11 5C3<> BA3<                                       | R                              | POS4 4B2<> 4C2<<br>SOF1 2C4<> 4D7> 5D3<                                                     |               |                                   |          |               |   |       |          |

| Н  | A13 5C3<> BA3<<br>A14 5B3<> BA3<                     |                                | S0F2 2A4<> 4D5> 5D3<<br>S0F3 2C2<> 4D3> 5D3<                                                |               |                                   |          |               |   |       | $\vdash$ |

| 11 | A15 6B3<> BA3<<br>AUX_CLK 6BB<> BD3<                 |                                | S0F4 2A2<> 4D1> 5D2<<br>ST 6B6<> 8B1<> 2C8< 3                                               | 3884 7014     |                                   |          |               |   |       | 1        |

|    | BRD_OSC BC5> BD3<>                                   | R                              | W_T                                                                                         | 3550 1610     |                                   |          |               |   |       | 1        |

|    | CFG_DIN 7A3> 7A3<>                                   | 8B1<> R                        | XN2 486< 588<                                                                               |               |                                   |          |               |   |       | 1        |

|    | CLK1544_T 6B2<><br>CLK163B4_T 6C4<>                  |                                | XN3 484< 5A8<<br>XN4 482< 5A8<                                                              |               |                                   |          |               |   |       |          |

| c  | CS1 8B1<> 2C8<<br>CS2 8B1<> 3B4<                     |                                | XP1 486 5D8 (XP2 486 5C8 (                                                                  |               |                                   |          |               |   |       | c '      |

|    | CS_T 6BB<> BC1< DØ 2C5<> 3C4<                        | 6B6<> 8D3<> R                  | XP3 4B4< 5BB<<br>XP4 4B2< 5AB<                                                              |               |                                   |          |               |   |       |          |

| 11 | D1 2C5<> 3C4<                                        | 6B6<> 8D3<> S                  | CLK 2CB< 8D2<                                                                               |               |                                   |          |               |   |       |          |

|    | D3 2C5<> 3C4<                                        | 6B6<> 8D3<> T                  |                                                                                             |               |                                   |          |               |   |       |          |

| 11 |                                                      |                                | 3 586<><br>3_CLK 3C8< 8D3<                                                                  |               |                                   |          |               |   |       |          |

|    | D6 2C5<> 3C4<                                        | 6B6<> 8D4<> T<br>6B6<> 8D4<> T |                                                                                             |               |                                   |          |               |   |       |          |

| П  | DONE 7A5< 7C1<                                       | т                              | CLK2 4D6> 4B5<                                                                              |               |                                   |          |               |   |       | Г        |

|    |                                                      | 688<> 8A3<> T                  | CLK3 4D5> 4B3<<br>CLK4 4D2> 4B1<                                                            |               |                                   |          |               |   |       |          |

|    | INT_IND 8A3<> 8B5< JTCLK 7A7<> 2B8<                  | 3C8< 7C1                       | DAT1 2D4<> 4D8< 5C5<<br>DAT2 2B4<> 4D6< 5C5<                                                |               |                                   |          |               |   |       |          |

|    | JTDI_CON2FRM 7A5<> 2B8<<br>JTD0_SPART2CON 7A5<> 7C1> | т                              | DAT3 2D2<> 4D5< 5B5 DAT4 2B2<> 4D2< 5B5<                                                    |               |                                   |          |               |   |       |          |

|    | JTD_FRM2LIU 288<> 7A8<                               | 3C8< T                         | DEN1 2D4<> 4C7> 5C1<                                                                        |               |                                   |          |               |   |       |          |

| В  | JTD_LIU2PROM 3CB> 7AB<><br>JTD_PROM2SPART 7A6<> 7AB< | 7D1< T                         | DEN2 2B4<> 4C5> 5C1<<br>DEN3 2D2<> 4C3> 5C1<                                                |               |                                   |          |               |   |       | В        |

|    | JTMS 7A7<> 2B8<<br>JTRST 7B8<> 2B8<                  |                                | DEN4 2B2<> 4C1> 5C1< TCLK1 2D4<> 4D8< 5C5<                                                  |               |                                   |          |               |   |       |          |

|    | PCM_RSYNC                                            |                                | ICLK2 2B4<> 4D6< 5C5< ICLK3 2D2<> 4D5< 5C5<                                                 |               |                                   |          |               |   |       |          |

|    | PCM_RXD                                              | т                              | ICLK4 2B2<> 4D2< 5C5< MEI 8A3<> 2C8<                                                        |               |                                   |          |               |   |       |          |

|    | PCM_TXCLK 6C8<> 5B1<                                 | т                              | NEG1 4C7> 4B7<                                                                              |               |                                   |          |               |   |       |          |

| Н  | PCM_TXD 6C8<> 5B1<<br>R1 5D6<>                       | Т                              | NEG2 4C5> 4B5<<br>NEG3 4C3> 4B3<                                                            |               |                                   |          |               |   |       | $\vdash$ |

|    | R2 505<> R3 586<>                                    |                                | NEG4 4C1> 4B1<<br>OH1 2C4<> 4D8< 5A3<                                                       |               |                                   |          |               |   |       | 1        |

| 11 | R4 5A5<> RCLK1 4B8<> 4C8<                            |                                | OH2 2B4<> 4D6< 5A3<<br>OH3 2C2<> 4D5< 5A3<                                                  |               |                                   |          |               |   |       | 1        |

| 11 | RCLK2 4B6<> 4C6<<br>RCLK3 4B4<> 4C5<                 | Т                              | OH4 2B2<> 4D2< 5A3<<br>OHEN1 2C4<> 4C8< 5A3<                                                |               |                                   |          |               |   |       | 1        |

| 11 | RCLK4 4B2<> 4C2<                                     | т                              | OHEN2 2B4<> 4C6< 5A3<                                                                       |               |                                   |          |               |   |       | 1        |

|    | RDAT1 2C4<> 4D7><br>RDAT2 2B4<> 4D5>                 | 585< T                         | OHEN3 2C2<> 4C5< 5A3<<br>OHEN4 2B2<> 4C2< 5A3<                                              |               |                                   |          |               |   |       |          |

| А  | RDAT3 2C2<> 4D3><br>RDAT4 2A2<> 4D1>                 |                                | P0S1 4C7> 4B7<<br>P0S2 4C5> 4B5<                                                            |               |                                   |          |               |   |       | А        |

|    | RDEN1 2C4<> 4D7><br>RDEN2 2A4<> 4D5>                 | 5D3< T                         | P053 4C3> 4B3<<br>P054 4C1> 4B1<                                                            |               |                                   |          |               |   |       |          |

| 11 | RDEN3 2C2<> 4D3>                                     | 5D3< T                         | S0F1 2D4<> 4C7<> 5A2<                                                                       |               |                                   |          |               |   |       | 1        |

|    | RDEN4 2A2<> 4D1> RD_DS 8B1<> 2C8<                    | 3B4< T                         | SOF2         2B4         4C5         5A2           SOF3         2C2         4C3         5A2 |               |                                   |          |               |   |       |          |

|    | RECU 2A2<> BA3<<br>RL0S1 4D7> BA5<>                  | Т                              | S0F4 2B2<> 4C1<> 5A2<<br>XN1 4B7<> 5D8<                                                     |               |                                   |          |               |   |       |          |

|    | RL0S2 4D5> 8A5<><br>RL0S3 4D3> 8A5<>                 |                                | XN2 4B5<> 5C8<<br>XN3 4B3<> 5B8<                                                            |               |                                   |          |               |   |       |          |

|    | RL0S4 4D1> 8A5<><br>RNEG1 4B8<> 4C8<                 | т                              | XN4 4B1<> 5AB XP1 4B7<> 5DB<                                                                |               |                                   | TI       | ITLE:         |   | DATE: | 1        |

|    | RNEG2 4B6<> 4C6<                                     |                                | XP2 4B5<> 5CB<                                                                              |               |                                   |          |               |   |       |          |

|    |                                                      |                                |                                                                                             |               |                                   | EI       | NGINEER:      |   | PAGE: | 1        |

| L  |                                                      | _                              | _                                                                                           | _             |                                   | _        |               |   |       | L        |

| 1  | 8                                                    | 7                              | 6                                                                                           | 5             | 4                                 | 3        |               | 2 | 1     |          |

|   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5        | 4 | 3         | 2 | 1     | $\neg$ |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|-----------|---|-------|--------|

| ם | *** Part Cross-Reference for  C1 CAP1 9D2  C2 CAP1 9D3  C3 CAP 9B3  C4 CAP 9B3  C5 CAP 9B5  C5 CAP 9B1  C7 CAP 9B2  C8 CAP 9B2  C8 CAP 9B2  C9 CAP 9B2  C10 CAP 9B3  C11 CAP 9B1  C12 CAP 9B5  C13 CAP 9B1  C12 CAP 9B5  C13 CAP 9B5  C14 CAP 9B5  C15 CAP 9B5  C16 CAP 9B1  C17 CAP 9B1  C18 CAP 9B5  C19 CAP 9B5  C19 CAP 9B5  C10 CAP 9B5  C10 CAP 9B5  C11 CAP 9B4  C14 CAP 9B4                                                                                                                                            | R<br>R R R R<br>R R R<br>R R<br>R R<br>R R<br>R R<br>R R<br>R R | 19 RES1 5A8 20 RES1 5B8 21 RES1 5D8 22 RES1 5D8 23 RES1 7A6 24 RES 9D4 25 RES1 8B6 26 RES1 8B6 27 RES 7B8 28 RES1 8D2 27 RES 7B8 28 RES1 8D3 30 RES1 5B1 31 RES1 5C4 32 RES1 5A3 33 RES1 5C4 44 RES1 5C4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |   |           |   |       | ם      |

| С | C15 CAP1 9D2 C16 CAP 9B2 C17 CAP 9B8 C18 CAP 9B2 C19 CAP 9B8 C20 CAP 9B4 C21 CAP 9D5 C22 CAP 9B5 C23 CAP 9B7 C24 CAP 9C4 C25 CAP 9B5 C26 CAP 9B5 C26 CAP 9B2 C27 CAP 9B3 C29 CAP 9B2 C31 CAP 9B6 C31 CAP 9B6 C31 CAP 9B6 C32 CAP 9B6 C31 CAP 9B6 C32 CAP 9B6 C31 CAP 9B6 C31 CAP 9B6 C32 CAP 9B6 C33 CAP 9B6 C33 CAP 9B6 C34 CAP 9B6 C35 CAP 9B6 C36 CAP 9B6 C37 CAP 9B6 C38 CAP 9B6 C39 CAP 9B6                                                       | R R R R R R R R R R R R R R R R R R R                           | 35 RESI SCI 36 RESI SC4 37 RESI SC4 38 RESI SC4 39 RESI SC1 40 RESI SCI 41 RESI SCI 42 RESI SA3 42 RESI SA3 43 RESI SCI 44 RESI SA3 44 RESI SCI 45 RESI SD3 47 RESI SD3 48 RESI SD3 49 RESI SD3 49 RESI SD3 40 RESI SD3 50 RESI SB4 50 RESI SD3 51 RESI SD3 52 RESI SD3 53 RESI SB4 52 RESI SD3 53 RESI SB4 52 RESI SD3 53 RESI SD3 54 RESI SD3 55 RESI SD3 55 RESI SD3 55 RESI SD3 55 RESI SD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   |           |   |       | С      |

| В | DS2 LED 842 DS3 LED 8A6 DS4 LED 8A7 DS5 LED 8A6 DS6 LED 847 DS7 LED 846 DS8 LED 847 DS9 LED 886 DS10 LED 887 J1 CONN_18P 787 J2 CONN_28P 2B3 J4 CONN_28P 2B2 J5 CONN_28P 2B2 J5 CONN_8NC_SPIN 5A5 J7 CONN_BNC_SPIN 5A5 J8 CONN_BNC_SPIN 5B5 J8 CONN_BNC_SPIN 5B5 J9 CONN_BNC_SPIN 5B5                                                                                                                                                                                                                                          | R R R R R R R R R R R R R R R R R R R                           | 54 RESI 5D2 55 RESI 5D3 55 RESI 5D3 56 RESI 5D3 57 RESI 5D3 58 RESI 5D3 60 RESI 5D3 60 RESI 50 |          |   |           |   |       | В      |

| Œ | J10 CONN_BNC_SPIN SCS J11 CONN_BNC_SPIN SCS J11 CONN_BNC_SPIN SCS J13 CONN_BNC_SPIN SCS J13 CONN_BNC_SPIN SCS J13 CONN_SPIS EDS J14 CONN_SPIS EDS J15 CONN_SPIS EDS R1 RES1 SCI R2 RES1 SB1 R3 RES1 SC1 R5 RES1 SC1 R6 RES 7C2 R7 RES1 SC1 R8 RES1 SC1 R9 RES1 SC1 R9 RES1 SC1 R9 RES1 SC1 R9 RES1 SC2 R10 RES1 SC4 R11 RES1 SC4 R11 RES1 SC4 R12 RES1 SC4 R15 RES1 SC4 R16 RES1 SC4 R17 RES1 SC4 R18 RES1 SC5 | R<br>T<br>T<br>T<br>U<br>U<br>U<br>U<br>U<br>U                  | 72 RESI SC8 1 XFNRXIE.JJ SC6 PI TESTPOINT 989 P2 TESTPOINT 984 P3 TESTPOINT 2A2 1 ATITUUS5 782 2 XCL8W22W044C_JJ 785 3 MX1792 904 4 XC2SS6_JJ SC3 7C3 BC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3<br>4BB |   | TITLE:    |   | DATE: | Œ      |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |   | ENGINEER: |   | PAGE: | ]      |

|   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5        | 4 | 3         | 2 | 1     | - 1    |